# onsemi

# eFuse, 4 Channel, 60 V, 2.5 A

# NIS3071, NIV3071

The NIS/NIV3071 is a 4-channel, 60 V, 2.5 A per channel eFuse which protects downstream loads from output shorts, overloads and overcurrent events. Each channel is in a high-side configuration, and is independently controlled by its corresponding enable pins. The NIS/NIV3071 communicates status via a common active-low fault pin. This eFuse features an internal soft start delay, trip time control, and an adjustable current limit setting common to all channels. The NIS3071 is well suited for industrial and telecom applications while the NIV3071 is for automotive applications.

## Features

- 4 Independent Channels with 2.5 A Current Capability Each

- Power Device Thermally Protected for Each Channel

- No External Current Shunt Required

- Active-High Digital Enable Pin

- Open-Drain Common Fault Pin

- Adjustable Overcurrent Limit for All Channels

- Adjustable Turn-on Time Control

- NIV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- These Devices are Pb-Free and are RoHS Compliant

# **Typical Applications**

- Automotive Body Control Modules

- Power Distribution Box

- Automotive Zonal Controllers

- Load/Harness Protection

- Automotive Low-Medium Power Loads

- General Purpose High-Side Load Switch

- Power Amplifier Protection

- Motor Drive Protection

- Telecomm Equipment

- 8 V to 60 V Industrial

WQFN16, 6x5 CASE 510CM

WQFNW16, 6x5 CASE 512AN

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 11 of this data sheet.

# NIS3071, NIV3071

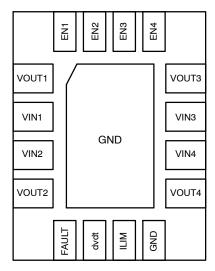

# Table 1. PIN FUNCTION DESCRIPTION

| Pin | Function | Description                                                                                                       |  |  |

|-----|----------|-------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | OUT1     | Output voltage for channel 1                                                                                      |  |  |

| 2   | IN1      | Input voltage for channel 1                                                                                       |  |  |

| 3   | IN2      | Input voltage for channel 2                                                                                       |  |  |

| 4   | OUT2     | Output voltage for channel 2                                                                                      |  |  |

| 5   | FAULT    | Active Low Open–Drain FAULT pin (Pull up to 5 V, 3.3 V or 1.8 V external logic supply with 15 $k\Omega$ resistor) |  |  |

| 6   | dvdt     | Turn-on Time control (connect capacitor to ground to control output slew rate)                                    |  |  |

| 7   | ILIM     | Connect R <sub>LIM</sub> resistor to GND to set current limit for all channels                                    |  |  |

| 8   | GND      | Ground                                                                                                            |  |  |

| 9   | OUT4     | Output voltage for channel 4                                                                                      |  |  |

| 10  | IN4      | Input voltage for channel 4                                                                                       |  |  |

| 11  | IN3      | Input voltage for channel 3                                                                                       |  |  |

| 12  | OUT3     | Output voltage for channel 3                                                                                      |  |  |

| 13  | EN4      | Channel 4 Enable, Active High, Internal Pull-up                                                                   |  |  |

| 14  | EN3      | Channel 3 Enable, Active High, Internal Pull-up                                                                   |  |  |

| 15  | EN2      | Channel 2 Enable, Active High, Internal Pull-up                                                                   |  |  |

| 16  | EN1      | Channel 1 Enable, Active High, Internal Pull-up                                                                   |  |  |

| PAD | GND      | Ground                                                                                                            |  |  |

#### Table 2. ABSOLUTE MAXIMUM RATINGS AND THERMAL RATINGS

| Rating                                                                                                         | Symbol                | Value                | Unit |

|----------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|------|

| IN1,2,3,4 Pins Input Voltage, operating, steady-state ( $V_{INx}$ , $V_{OUTx}$ to GND, Note 1)                 | V <sub>IN(Max)</sub>  | -0.3 to 60           | V    |

| Absolute Maximum Transient voltage on IN1,2,3,4 pins (Note 2)                                                  | V <sub>IN(Tran)</sub> | 65                   | V    |

| Maximum DC voltage on EN pin                                                                                   | V <sub>EN(Max)</sub>  | -0.3 to 6            | V    |

| Thermal Resistance, Junction-to-Air<br>JEDEC JESD51-5<br>JEDEC JESD51-7<br>0.5 in <sup>2</sup> copper (Note 3) | $\theta_{JA}$         | 32.1<br>56.8<br>24.0 | °C/W |

| Thermal Resistance, Junction-to-Lead                                                                           | θ <sub>JL</sub>       | 0.5                  | °C/W |

| Operating Junction Temperature Range (Note 4)                                                                  | Τ <sub>J</sub>        | -40 to 150           | °C   |

| Non-operating Junction Temperature Range                                                                       | ТJ                    | -50 to 155           | °C   |

| Lead Temperature, Soldering (10 sec)                                                                           | Τ <sub>L</sub>        | 260                  | °C   |

| ESD Human Body Model ANSI/ESDA/JEDEC JS-001 Class 2                                                            | ESD <sub>HBM</sub>    | 2.0                  | kV   |

| ESD Charged Device Model AEC Standard Q100-01 (JESD22-C101E)                                                   | ESD <sub>CDM</sub>    | 1.0                  | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

Negative voltage will not damage device provided that the power dissipation is limited to the rated allowable power for the package.

Transient Voltage pulse duration ≤ 100 μs.

Based on thermal models using the NIS/NIV3071 EVB.

Thermal limit is set above the maximum thermal rating. It is not recommended to operate this device at temperatures greater than maximum entire focus for the package is device the maximum thermal rating.

ratings for extended periods of time.

# NIS3071, NIV3071

#### **Table 3. ELECTRICAL CHARACTERISTICS**

(Unless otherwise noted: V<sub>IN</sub> = 48 V, C<sub>IN</sub> = 100  $\mu$ F, C<sub>OUT</sub> = 100  $\mu$ F, dV/dt pin open, R<sub>LIM</sub> = 20 kΩ, T<sub>A</sub> = 25°C)

| Characteristics                                                                                                                  | Symbol                   | Min | Тур                 | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----|---------------------|------|------|

| POWER FET                                                                                                                        |                          |     | -                   |      |      |

| ON Resistance per channel, $T_J = 25^{\circ}C$                                                                                   | R <sub>DS(ON)</sub>      |     | 80                  | 92   | mΩ   |

| ON Resistance per channel, T <sub>J</sub> = 150°C                                                                                | R <sub>DS(ON)</sub>      |     | 135                 | 155  |      |

| Continuous Current per channel (T <sub>A</sub> = 100°C, single channel)                                                          | I <sub>D(Cont)</sub>     |     | 2.5*                |      | Α    |

| Off State Leakage per channel ( $V_{IN}$ = 48 V, $V_{EN}$ = 0 V)                                                                 | I <sub>OFF</sub>         |     | 1.0                 |      | μA   |

| THERMAL LATCH                                                                                                                    | •                        | -   |                     |      | -    |

| Shutdown Temperature                                                                                                             | T <sub>SD</sub>          |     | 175                 |      | °C   |

| Thermal Hysteresis (Decrease in die temperature for turn on)                                                                     | T <sub>Hyst</sub>        |     | 27                  |      | °C   |

| OVERCURRENT PROTECTION                                                                                                           |                          |     |                     | -    |      |

| Minimum Settable Current Limit ( $R_{LIM}$ = 130 k $\Omega$ )                                                                    | I <sub>TH(Min)</sub>     |     | 0.5                 |      | А    |

| Threshold Current Level ( $R_{LIM}$ = 30 k $\Omega$ )                                                                            | I <sub>TH</sub>          | 1.9 | 2.0                 | 2.1  | Α    |

| Circuit Breaker Current Level                                                                                                    | I <sub>CB</sub>          |     | 2 x I <sub>TH</sub> |      | Α    |

| Circuit Breaker Response Time                                                                                                    | t <sub>CB</sub>          |     | 6                   |      | μs   |

| Overcurrent Trip Timer                                                                                                           | t <sub>TRIP</sub>        | 1.5 |                     |      | ms   |

| UNDERVOLTAGE LOCKOUT                                                                                                             |                          |     |                     |      |      |

| Undervoltage Lockout Level Rising                                                                                                | V <sub>UVLO</sub>        | 5.0 | 6.0                 | 7.0  | V    |

| Undervoltage Lockout Hysteresis                                                                                                  | UVLO <sub>hyst</sub>     |     | 0.3                 |      | V    |

| Undervoltage Lockout Response Time<br>(Time from Vin reaching UVLO to enabling/disabling)                                        | t <sub>UVLO</sub>        |     | 5.0                 | 10   | μs   |

| TURN-ON TIME                                                                                                                     |                          |     |                     | -    |      |

| Output On Delay Time (C <sub>IN</sub> = 100 $\mu$ F, C <sub>OUT</sub> = none, V <sub>IN</sub> = 48 V) (Note 5)                   | t <sub>DLY(On)</sub>     |     | 350                 |      | μs   |

| Turn–On Time (C <sub>IN</sub> = 100 $\mu$ F, C <sub>OUT</sub> = none, V <sub>IN</sub> = 48 V, C <sub>dvdt</sub> = none) (Note 5) | t <sub>RAMP(On)</sub>    |     | 1.5                 |      | ms   |

| LOGIC INPUT/OUTPUT                                                                                                               |                          | _   |                     |      | _    |

| LOW Level Input; EN                                                                                                              | VIL                      |     |                     | 0.4  | V    |

| HIGH Level Input; EN                                                                                                             | V <sub>IH</sub>          | 1.2 |                     |      | V    |

| LOW Level Output; FAULT, 0.5 mA                                                                                                  | V <sub>OL</sub>          |     |                     | 0.3  | V    |

| Output Sink Current; FAULT                                                                                                       | I <sub>OL</sub>          |     |                     | 0.5  | mA   |

| EN Sink Ground Current; EN (V <sub>IN</sub> = 48, ENx = 0 V)                                                                     | I <sub>EN(sink)</sub>    |     | 3                   |      | μA   |

| EN Pull-up Current (EN = 5 V)                                                                                                    | I <sub>EN(pull-up)</sub> |     |                     | 1    | μΑ   |

| TOTAL DEVICE CURRENT                                                                                                             |                          |     |                     |      |      |

| Off State Bias Current (All channels Off)                                                                                        | I <sub>bias(Off)</sub>   |     | 85                  | 175  | μA   |

| On State Bias Current (All channels On, No Load)                                                                                 | I <sub>bias(On)</sub>    |     | 850                 | 1200 | μA   |

|                                                                                                                                  |                          | 1   | 1                   | T    |      |

On State Bias Current (All channels On, 2.5 A load per channel) 5.0 mΑ I<sub>bias(On,Max)</sub> Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions. \*Application is to have  $R_{\theta JA} \leq 14^{\circ}$ C/W when driving 2.5 A on each channel.

5. 1 A load connected to output.

NIS3071, NIV3071

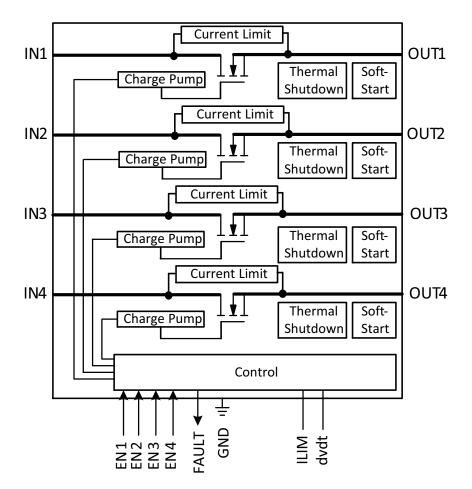

Figure 1. Block Diagram

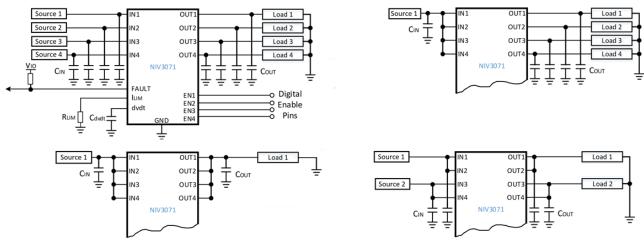

### **APPLICATIONS INFORMATION**

#### **Basic Operation**

The NIS/NIV3071 is an eFuse with four self-protected channels in a high-side configuration. It contains circuits to monitor the output current and die temperature for each channel independently.

Once the input voltage is applied to any INx pin, the device will apply the input voltage to the load connected to OUTx pin based on the restrictions of the controlling circuits. It is also possible to operate this eFuse with common inputs and common outputs, thus paralleling the channels for higher total output current. When a channel is not in use connect the INx and ENx pins to ground.

Each channel of the device will remain on as long as the temperature of the channel FET does not exceed the 175°C limit that is programmed into the chip.

The overcurrent protection circuit will allow for a load to draw the current for that channel within the allowable overcurrent limit defined by  $I_{TH}$  and  $I_{CB}$ . If the load current in one channel exceeds limits defined by  $I_{TH}$  and  $I_{CB}$  it will subsequently turn off, while other channels can continue the normal operation.

An internal charge pump provides bias for the gate voltage of the internal power FET structures and also for the current limit circuit. The remainder of the control circuitry operates between the input voltage at INx pins and ground.

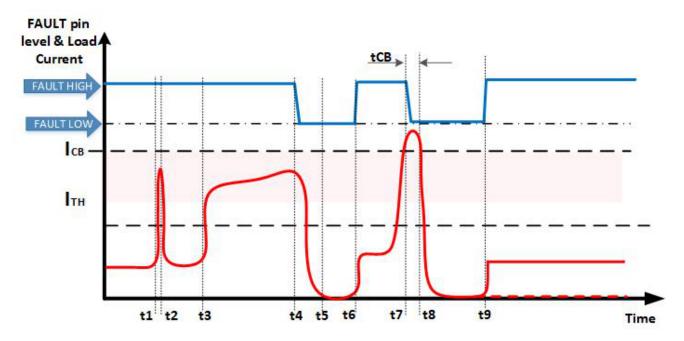

#### **Overcurrent Protection**

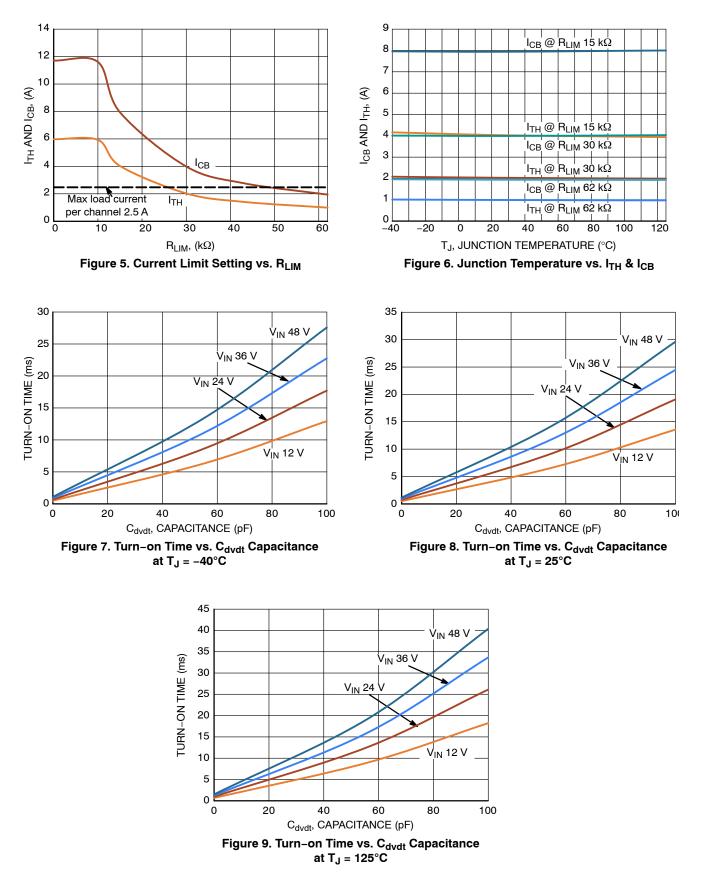

The Overcurrent protection circuit monitors the load current and allows the load to draw current as long as its level is within an allowable overcurrent range defined by ITH and I<sub>CB</sub>. The I<sub>TH</sub> is the overcurrent limit set by the R<sub>LIM</sub> resistor, and ICB is a circuit breaker level which is 2x of ITH; as long as the load is drawing current not exceeding the ICB level the FET is on, if the current level exceeds the  $\ensuremath{I_{\text{CB}}}$  level the FET is turned off for that specific channel. If during the overcurrent mode the internal temperature for the channel FET exceeds the threshold level, that specific channel will be shut off. Additional device options offer a overcurrent trip timer which starts counting right after the load current exceeds the I<sub>TH</sub> level, once the predetermined amount of time has elapsed the channel will be shut off. Examples of a typical operation for such scheme is shown in Figure 4. Figure 5 shows typical values of I<sub>TH</sub> with respect to the RLIM resistor.

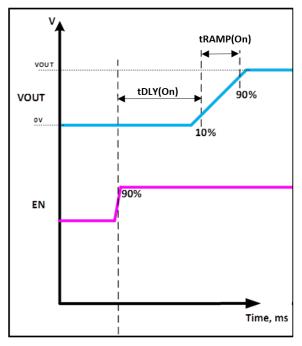

#### Turn-on Time Control

The Turn-on Time circuit brings the output voltage up under a linear controlled rate. The default ramp time is approximately 1.5 ms. This can be modified by adding an external capacitor at the dvdt pin.

The diagram showing the typical turn–on time and enable delay is shown in Figure 3. The value of capacitor connected to dvdt pin defines the  $t_{RAMP(On)}$  turn on times as shown in a Figures 7, 8 and 9. It is recommended to use a ceramic or other low leakage capacitor.

#### Enable

The active high Enable pins provides a digital interface to control the state of the channels. When ENx pin is pulled low by external circuitry, the specific channel will be turned off. When ENx pin is driven high or left floating, the corresponding channel is enabled. In applications with high inductances on the output, it is recommended to pull the ENx pins high. Protection circuits such as the overcurrent limit function override the function of the enable pin. The EN pin has an internal high impedance pull–up resistor.

#### Fault

The FAULT pin is an open-drain active low pin signaling the system controller about an overcurrent event on any of the channels. If a thermal shutdown or overcurrent trip timer runout event occurs, the FAULT pin will be pulled low. After the fault is cleared the pin will be floating or pulled up by an external pull-up resistor. The pin can be left unconnected if not used.

| Condition                                        | Fault Pin Status<br>(With external pull up) |

|--------------------------------------------------|---------------------------------------------|

| Thermal Shutdown                                 | Low                                         |

| I <sub>CB</sub> Overcurrent Event                | Low                                         |

| I <sub>TH</sub> Overcurrent Event<br>(t > tTrip) | Low                                         |

| Normal Operation                                 | High                                        |

| Input < UVLO                                     | High                                        |

#### Table 4. FAULT PIN TRUTH TABLE

## **Thermal Protection**

The NIS/NIV3071 series device includes an independent internal temperature sensing circuit for each channel that senses the temperature of the power FETs on the die. If the FET temperature reaches 175°C for any of the channels, the device will shut down that specific channel while other channels will continue normal operation. The disabled channel will be automatically turned on once the channel FET temperature has been reduced by 27°C. (for auto–retry version, latched version must be reset) The thermal limit has been set high intentionally, to increase the trip time during high power transient events. It is not recommended to operate this device above 150°C in normal operating conditions.

#### **Transient Protection**

In the event of a short circuit or overcurrent fault, the device will interrupt the flow of current by becoming an open circuit. If there is inductance in the system, specifically on the input or output pins of the eFuse, the resulting transients could exceed the datasheet maximum voltage ratings. Input inductance will generate a positive voltage spike on the INx pin(s) and output inductance will generate a negative voltage spike on the OUTx pin(s). Some applications may require large inductances on the input or output, in such a case a Transient Voltage Suppressor (TVS) can placed between the input and ground pins and a Schottky diode can be placed between the output and ground pins to maintain the datasheet absolute maximum voltage ratings. Additionally, capacitors can be used to help absorb transients as well.

Figure 3. Turn On Delay and Turn-on Time

t1: Current is above  $I_{TH}$  (but below  $I_{CB}); t_{TRIP}$  counter is started.

t2: Current goes below I<sub>TH</sub> before t<sub>TRIP</sub> timer expires. t<sub>TRIP</sub> counter is reset and normal operation continues.

t3: Current is above  $I_{TH}$  (but below  $I_{CB}$ );  $t_{TRIP}$  counter is started. Note that the load continues to draw current as long as it is below  $I_{CB}$  and device remains below the thermal shutdown temperature ( $T_{SD}$ ).

t4: Device begins shut down due to A) t<sub>TRIP</sub> timer has expired, OR B) device has reached the thermal shutdown temperature (T<sub>SD</sub>). FAULT pin is pulled low. t5: Device shuts down in t<sub>TSD</sub> after t4.

t6: Device is restarted when temperature is reduced by 27°C (Auto-Retry version only; Latched version will require manual restart with EN pin).

t7: Device output has been shorted (or a severe current overload condition).

t8: Device Output current has exceeded  $I_{CB}$ . The device is immediately shut down within the  $I_{CB}$  shutdown time  $t_{CB}$ . FAULT pin is pulled low.

t9: Device restarts after auto-retry time is exceeded (Auto-Retry only, Latch version will require a manual restart with EN).

Note: dotted line shows device remains off for latched version (until restarted using EN pin).

#### Figure 4. Overcurrent Protection Diagram

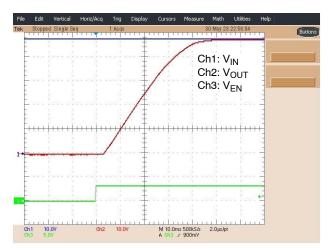

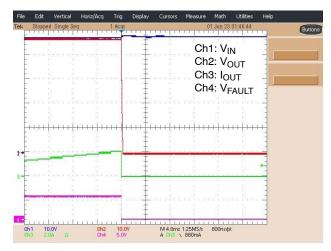

Figure 10. Turning on a Single Output with EN Pin

Figure 12. Turning on a Single Output with the Input Voltage (EN pin pull-up or floated)

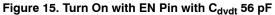

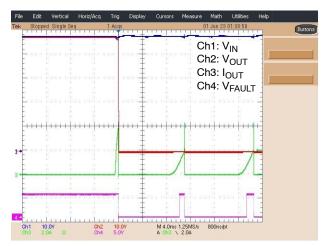

Figure 14. Turn On with EN Pin with Cdvdt Open

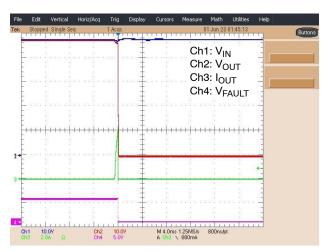

Figure 11. Turning on a Single Output with the EN Pin While Another Output Pin is On

Figure 13. Turning on a Single Output with the Input Voltage While Another Output is On (EN pin pull-up or floated)

Figure 16. I<sub>TH</sub> Overcurrent Event on Latching Device

Figure 18. I<sub>CB</sub> Overcurrent Event on Latching Device

Figure 20. Short Circuit Event on Latching Device

Figure 17. I<sub>TH</sub> Overcurrent Event on Auto-retry Device

Figure 19. I<sub>CB</sub> Overcurrent Event on Auto-retry Device

Figure 21. Short Circuit Event on Auto-retry Device

Figure 22. I<sub>TH</sub> Overcurrent Event While Another Output is On

Figure 23. I<sub>CB</sub> Overcurrent Event While Another Output is On

#### **ORDERING INFORMATION**

| Part Number     | Shutdown Version | Package                                         | Shipping <sup>†</sup> |

|-----------------|------------------|-------------------------------------------------|-----------------------|

| NIS3071MT3TWG   | Latch            | WQFN16 5x6 mm<br>(Pb-Free)                      | 5000 / Tape & Reel    |

| NIS3071MT4TWG   | Auto-R           | WQFN16 5x6 mm<br>(Pb-Free)                      | 5000 / Tape & Reel    |

| NIV3071MTW3TWG* | Latch            | WQFNW16 5x6 mm<br>(Pb–Free)<br>(Wettable Flank) | 5000 / Tape & Reel    |

| NIV3071MTW4TWG* | Auto-R           | WQFNW16 5x6 mm<br>(Pb–Free)<br>(Wettable Flank) | 5000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

\*NIV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC–Q101 Qualified and PPAP Capable.

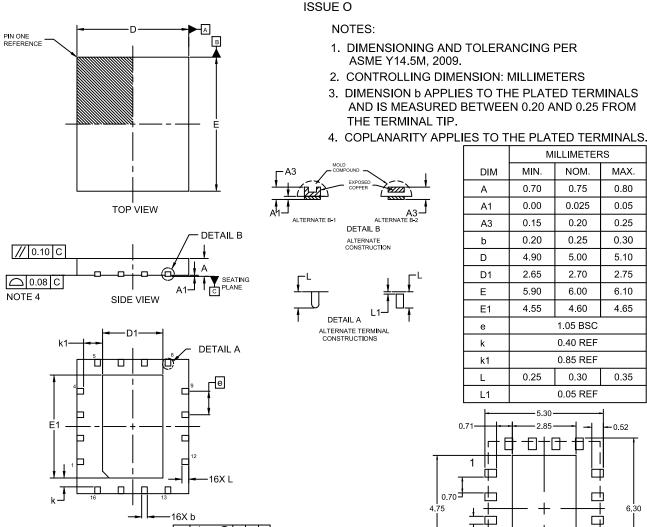

# PACKAGE DIMENSIONS

WQFN16 5x6, 1.05P CASE 510CM

Ø0.10 (CAB

Ø0.05M C

¢

NOTE 3

BOTTOM VIEW

ΨĴ

ഥ

П

山

피누다

RECOMMENDED MOUNTING PATTERN For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

0.35

#### NIS3071, NIV3071

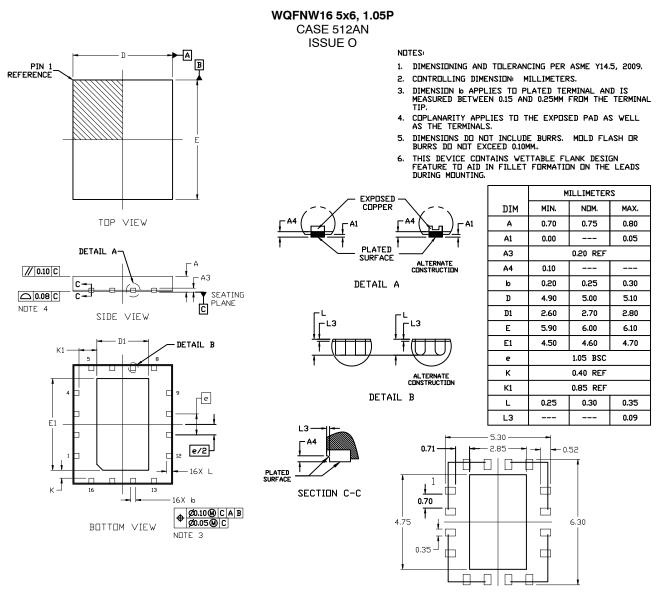

#### PACKAGE DIMENSIONS

RECOMMENDED MOUNTING PATTERN

\* For additional information on our Pb-Free strategy and soldering details, please download the UN Semiconductor Soldering and Mounting Techniques Reference Manual, SULDERRM/D.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-1s" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specification scan and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such

#### ADDITIONAL INFORMATION

#### TECHNICAL PUBLICATIONS:

Technical Library: <u>www.onsemi.com/design/resources/technical-documentation</u> onsemi Website: <u>www.onsemi.com</u>

#### ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales